# X-1500 Reference Manual

# Contents

#### 4 Introduction

Block Diagram of the X-1500 Package contents Getting started

#### 10 Overview

X-1500 User interface X-1500 LED's, buttons, & jumpers

#### 10 Pin out descriptions

X300: Communication connector J440: Analog input connector J500: I/O extension connector

J600: Memory extension connector

Contents 3

### Introduction

Congratulations on your purchase of the Si-Gate X-1500 Configurable Automotive ECU Platform. The X-1500 provides designers with a configurable ECU right out of the box suitable for a wide range of Automotive and Industrial applications. Please review the following reference manual thoroughly to receive the most of your new purchase.

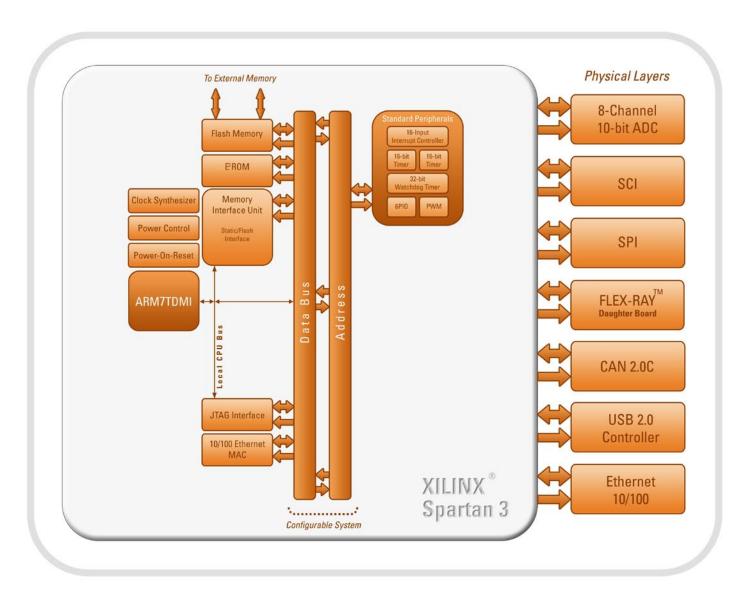

The X-1500 is a complete 32-bit Field Configurable ECU platform, combining the highly popular 32-bit ARM7TDMI-S™ or Xilinx MicroBlaze™ processor core with standard System-on-Chip peripherals and over 150 user programmable I/O's. It is contained within a Xilinx Spartan-3™ FPGA with programmable logic for custom driven IP applications, a robust memory subsystem, and a full suite of Automotive and Industrial peripherals. The X-1500 enables programmable System-on-Chip applications and expands traditional development platforms by including necessary physical layers on-board the ECU. The X-1500 supports physical layers for 10/100 Ethernet, JTAG, USB 2.0, 12-bit ADC, High and Low Speed CAN, FlexRay™, LIN, K-Line, UART, and SPI along with on-board Flash and SRAM memory.

The X-1500 is ideal for projects where flexibility and expand-ability is needed for your future ECU developments. Please visit <a href="https://www.si-gate.com">www.si-gate.com</a> for additional or updated information which may not be presented in this manual.

**Block diagram of the Si-Gate X-1500**

Introduction 5

## **Package Contents**

### Your X-1500 Development kit includes the following components:

Users Manual

Installation CD

Mains Adapter

USB A/B Cable

**Ethernet Cable**

### **Getting Started**

The standard bit stream that is delivered with the Si-Gate X-1500 includes a Xilinx Microblaze Soft Core. This is integrated with a basic RS-232 demo application which provides the user the ability to immediately connect the X-1500 to a PC serial port and start developing. When coupled together with the Xilinx EDK toolchain (must be purchased seperately) the X-1500 development kit provides everything the user needs to start writing software for Microblaze inside the Spartan-3 FPGA. If the user wants to develop new bit streams, this can be done with the purchase of the Xilinx ISE Foundation. Or the user may opt for a Si-Gate specialist to handle this integration task leaving room for the user to concentrate on their specific applications.

#### Communicating with the X-1500

Because of the constant challenge in deciding which peripherals are needed in a new automotive system, several physical layers are included with the X-1500 which allow the user to add peripherals of their choice at any time without having to re-design the hardware interfaces including:

**CAN 2.0C**

ETHERNET 10/100 Part # LXT971 (Ethernet MAC needed inside FPGA for operation) USB 2.0 Controller Part # CY7C68001

SPI

SCI

12 bit ADC

With the X-1500's FPGA architecture, the user has the complete flexibility to select any combinations of automotive periphals, memory, and interface features that give the best system performance at the lowest costs on a single FPGA.

#### **Xilinx MicroBlaze Soft Processor Core**

The MicroBlaze core is a 3-stage pipeline 32-bit RISC Harvard architecture soft processor core with 32 general purpose registers, ALU, and rich instruction set optimized for embedded applications. It supports both on-chip block RAM and/or external memory.

This basic design can then be configured with more advanced features such as: barrel shifter, floating-point unit (FPU), caches, exception handling, debug logic, and others. This flexibility allows the user to balance the required performance of the target application against the logic area cost of the soft processor. Additional information can be found at <a href="https://www.xilinx.com">www.xilinx.com</a>.

Introduction

## **Overview**

The following section will inform you on the basic components of the X-1500.

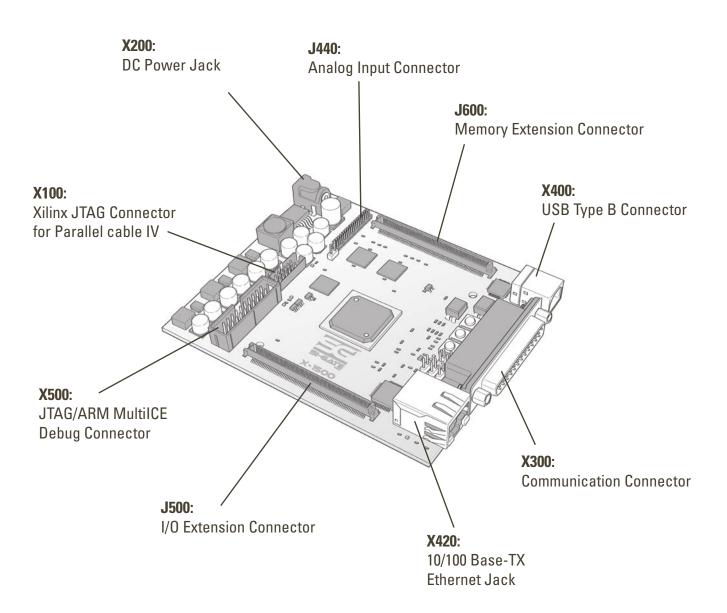

| X-1500 User Interface                                    |                                                       |

|----------------------------------------------------------|-------------------------------------------------------|

| X200: DC Power Jack                                      | Connect the supplied mains adapter here               |

| J440: Analog Input Connector                             | See pin out descriptions on page 13                   |

| J600: Memory Extension Connector                         | See pin out descriptions on page 15                   |

| X400: USB Type B Connector                               |                                                       |

| X300: Communication Connector                            | See pin out descriptions on page 12                   |

| X420: 10/100 Base-TX Ethernet Jack                       |                                                       |

| J-500: I/O Extension Connector                           | See pin out descriptions on page 14                   |

| X500: JTAG/ARM MultiICE Debug Connector                  | Additional information can be found at www.arm.com    |

| <b>X100:</b> Xilinx JTAG Connector for Parallel cable IV | Additional information can be found at www.xilinx.com |

Overview 9

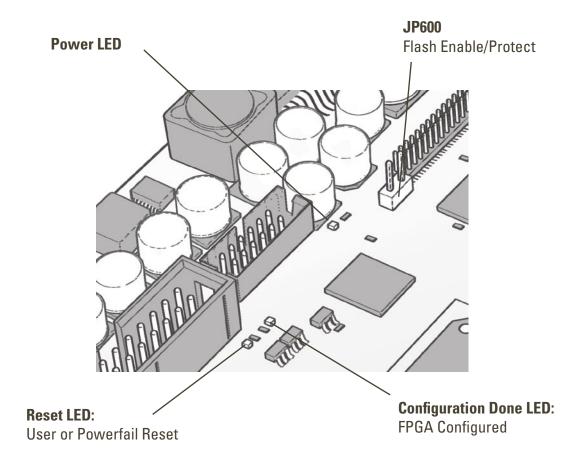

| X-1500 LED's, Buttons, & Jumpers    |                                                                   |  |  |

|-------------------------------------|-------------------------------------------------------------------|--|--|

| Power LED                           | Indicates power is being supplied to the X-1500                   |  |  |

| JP600: Flash Enable/Protect         | Stuff to enable flash erase or programming                        |  |  |

| Reset LED: User or Power Fail Reset | Indicates power failure, power on or user reset                   |  |  |

| Config Done LED: FPGA Configured    | Indicates that FPGA is configured                                 |  |  |

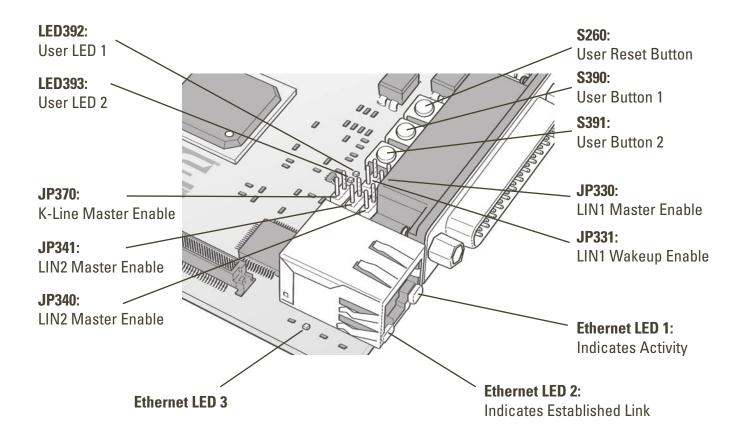

| <b>LED 392</b> : User LED 1         | User programmable LED 1                                           |  |  |

| <b>LED 393</b> : User LED 2         | User programmable LED 2                                           |  |  |

| JP370: K-Line Master                | Stuff for K-Line master mode                                      |  |  |

| JP341: LIN2 Master Enable           | Stuff to enable LIN2 master configuration                         |  |  |

| JP340: LIN2 Master Enable           | Stuff to enable LIN2 wakeup                                       |  |  |

| Ethernet LED 3                      | User programmable LED of ethernet PHY                             |  |  |

| <b>S260:</b> User Reset Button      | Manual reset button                                               |  |  |

| \$390: User Button 1                | User programmable push button 1                                   |  |  |

| S391: User Button 2                 | User programmable push button 2                                   |  |  |

| JP330: LIN1 Master Enable           | Stuff to enable LIN 1 master configuration                        |  |  |

| JP331: LIN1 Wakeup Enable           | Stuff to enable LIN 1 wakeup                                      |  |  |

| Ethernet LED 1                      | User programmable LED of ethernet PHY (default shows activity)    |  |  |

| Ethernet LED 2                      | User programmable LED of ethernet PHY (default shows link status) |  |  |

Overview 11

# Pin Out Descriptions

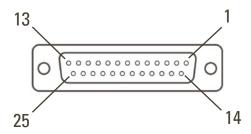

#### X300:

**Communication Connector**

| Pin | Signal    |

|-----|-----------|

| 1   | +12V      |

| 2   | IN_J1850  |

| 3   | GND       |

| 4   | IN_CAN1_H |

| 5   | IN_CAN1_L |

| 6   | GND       |

| 7   | IN_CAN2_H |

| 8   | IN_CAN2_L |

| 9   | GND       |

| 10  | LIN1_LINE |

| 11  | GND       |

| 12  | LIN2_LINE |

| 13  | GND       |

| 14  | KL_LINE   |

| 15  | GND       |

| 16  | CANB_H    |

| 17  | CANB_L    |

| 18  | GND       |

| 19  | RS0_TX    |

| 20  | RS0_RX    |

| 21  | RS1_TX    |

| 22  | RS1_RX    |

| 23  | RS2_TX    |

| 24  | RS2_RX    |

| 25  | GND       |

**J440:** Analog Input Connector

| Signal | Pin | Pin | Signal  |

|--------|-----|-----|---------|

| GNDA   | 2   | 1   | AN0     |

| GNDA   | 4   | 3   | AN1     |

| GNDA   | 6   | 5   | AN2     |

| GNDA   | 8   | 7   | AN3     |

| GNDA   | 10  | 9   | AN4     |

| GNDA   | 12  | 11  | AN5     |

| GNDA   | 14  | 13  | AN6     |

| GNDA   | 16  | 15  | AN7     |

| GNDA   | 18  | 17  | AN8     |

| GNDA   | 20  | 19  | AN9     |

| GNDA   | 22  | 21  | AN10    |

| GNDA   | 24  | 23  | AN11    |

| GNDA   | 26  | 25  | AN12    |

| GNDA   | 28  | 27  | AN13    |

| GNDA   | 30  | 29  | AN14    |

| GNDA   | 32  | 31  | AN15    |

| GNDA   | 34  | 33  | VDDA+5V |

| GNDA   | 36  | 35  | VDDA+5V |

| GNDA   | 38  | 37  | VDDA+5V |

| GNDA   | 40  | 39  | VDDA+5V |

Pin Out Descriptions

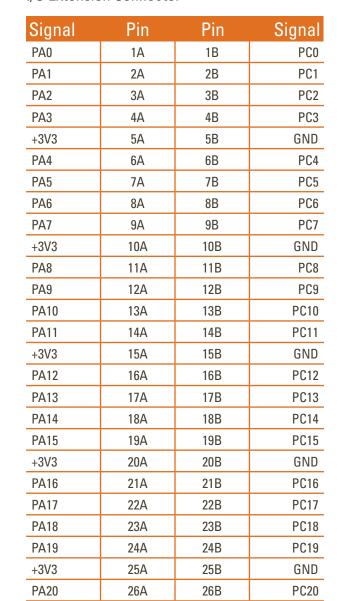

#### J500:

#### I/O Extension Connector

| Signal | Pin | Pin | Signal |

|--------|-----|-----|--------|

| PB0    | 41A | 41B | PD0    |

| PB1    | 42A | 42B | PD1    |

| PB2    | 43A | 43B | PD2    |

| PB3    | 44A | 44B | PD3    |

| +1V2   | 45A | 45B | GND    |

| PB4    | 46A | 46B | PD4    |

| PB5    | 47A | 47B | PD5    |

| PB6    | 48A | 48B | PD6    |

| PB7    | 49A | 49B | PD7    |

| +1V2   | 50A | 50B | GND    |

| PB8    | 51A | 51B | PD8    |

| PB9    | 52A | 52B | PD9    |

| PB10   | 53A | 53B | PD10   |

| PB11   | 54A | 54B | PD11   |

| +1V2   | 55A | 55B | GND    |

| PB12   | 56A | 56B | PD12   |

| PB13   | 57A | 57B | PD13   |

| PB14   | 58A | 58B | PD14   |

| PB15   | 59A | 59B | PD15   |

| +1V2   | 60A | 60B | GND    |

| PB16   | 61A | 61B | PD16   |

| PB17   | 62A | 62B | PD17   |

| PB18   | 63A | 63B | PD18   |

| PB19   | 64A | 64B | PD19   |

| +1V2   | 65A | 65B | GND    |

| PB20   | 66A | 66B | PD20   |

| PB21   | 67A | 67B | PD21   |

| PB22   | 68A | 68B | PD22   |

| PB23   | 69A | 69B | PD23   |

| +1V2   | 70A | 70B | GND    |

| PB24   | 71A | 71B | PD24   |

| PB25   | 72A | 72B | PD25   |

| PB26   | 73A | 73B | PD26   |

| PB27   | 74A | 74B | PD27   |

| +1V2   | 75A | 75B | GND    |

| PB28   | 76A | 76B | PD28   |

| PB29   | 77A | 77B | PD29   |

| PB30   | 78A | 78B | PD30   |

| PB31   | 79A | 79B | PD31   |

| +1V2   | 80A | 80B | GND    |

PA21

PA22

PA23

+3V3

PA24

PA25

PA26

PA27

+3V3

PA28

PA29

PA30

PA31

+3V3

27A

28A

29A

30A

31A

32A

33A

34A

35A

36A

37A

38A

39A

40A

27B

28B

29B

30B

31B

32B

33B

34B

35B

36B

37B

38B

39B

40B

PC21

PC22

PC23

GND

PC24

PC25

PC26

PC27

GND

PC28

PC29

PC30

PC31 GND

#### **J600**:

I/O Extension Connector

| Signal | Pin | Pin | Signal     |

|--------|-----|-----|------------|

| BD0    | 1C  | 1D  | MEM_#RD    |

| BD1    | 2C  | 2D  | MEM_#0E    |

| BD2    | 3C  | 3D  | MEM_#WE    |

| BD3    | 4C  | 4D  | UNUSED     |

| +5V    | 5C  | 5D  | GND        |

| BD4    | 6C  | 6D  | MEM_#BE3   |

| BD5    | 7C  | 7D  | MEM_#BE2   |

| BD6    | 8C  | 8D  | MEM_#BE1   |

| BD7    | 9C  | 9D  | MEM_#BE0   |

| +5V    | 10C | 10D | GND        |

| BD8    | 11C | 11D | SRAM_#CS   |

| BD9    | 12C | 12D | FLASH_#CS  |

| BD10   | 13C | 13D | FLASH_#RP  |

| BD11   | 14C | 14D | FLASH_STS  |

| +5V    | 15C | 15D | GND        |

| BD12   | 16C | 16D | BD12       |

| BD13   | 17C | 17D | USB_#RESET |

| BD14   | 18C | 18D | USB_#IFCLK |

| BD15   | 19C | 19D | USB_#INT   |

| +5V    | 20C | 20D | GND        |

| BD16   | 21C | 21D | USB_WAKEUP |

| BD17   | 22C | 22D | USB_READY  |

| BD18   | 23C | 23D | USB_FLAGA  |

| BD19   | 24C | 24D | USB_FLAGB  |

| +5V    | 25C | 25D | GND        |

| BD20   | 26C | 26D | USB_FLAGC  |

| BD21   | 27C | 27D | USB_PKTEND |

| BD22   | 28C | 28D | EXT1_#CS   |

| BD23   | 29C | 29D | EXT2_#CS   |

| +5V    | 30C | 30D | GND        |

| BD24   | 31C | 31D | TPX1       |

| BD25   | 32C | 32D | TPX2       |

| BD26   | 33C | 33D | SPI_#CS2   |

| BD27   | 34C | 34D | SPI_#CS1   |

| +5V    | 35C | 35D | GND        |

| BD28   | 36C | 36D | SPI_#CS0   |

| BD29   | 37C | 37D | SPI_SCLK   |

| BD30   | 38C | 38D | SPI_MOSI   |

| BD31   | 39C | 39D | SPI_MISO   |

| +5V    | 40C | 40D | GND        |

| Signal | Pin | Pin | Signal  |

|--------|-----|-----|---------|

| BA31   | 41C | 41D | PEXT4   |

| BA30   | 42C | 42D | PEXT5   |

| BA29   | 43C | 43D | PEXT6   |

| BA28   | 44C | 44D | PEXT7   |

| +2V5   | 45C | 45D | GND     |

| BA27   | 46C | 46D | PEXT8   |

| BA26   | 47C | 47D | PEXT9   |

| BA25   | 48C | 48D | PEXT10  |

| BA24   | 49C | 49D | PEXT11  |

| +2V5   | 50C | 50D | GND     |

| BA23   | 51C | 51D | PEXT12  |

| BA22   | 52C | 52D | PEXT13  |

| BA21   | 53C | 53D | PEXT14  |

| BA20   | 54C | 54D | PEXT15  |

| +2V5   | 55C | 55D | GND     |

| BA19   | 56C | 56D | PEXT16  |

| BA18   | 57C | 57D | PEXT17  |

| BA17   | 58C | 58D | PEXT18  |

| BA16   | 59C | 59D | PEXT19  |

| +2V5   | 60C | 60D | GND     |

| BA15   | 61C | 61D | PEXT20  |

| BA14   | 62C | 62D | PEXT21  |

| BA13   | 63C | 63D | PEXT22  |

| BA12   | 64C | 64D | PEXT23  |

| +2V5   | 65C | 65D | GND     |

| BA11   | 66C | 66D | PEXT24  |

| BA10   | 67C | 67D | PEXT25  |

| BA9    | 68C | 68D | PEXT26  |

| BA8    | 69C | 69D | PEXT27  |

| +2V5   | 70C | 70D | GND     |

| BA7    | 71C | 71D | PEXT28  |

| BA6    | 72C | 72D | PEXT29  |

| BA5    | 73C | 73D | PEXT30  |

| BA4    | 74C | 74D | PEXT31  |

| +2V5   | 75C | 75D | GND     |

| BA3    | 76C | 76D | VSUPPLY |

| BA2    | 77C | 77D | VSUPPLY |

| BA1    | 78C | 78D | VSUPPLY |

| BA0    | 79C | 79D | VSUPPLY |

| +2V5   | 80C | 80D | GND     |

Pin Out Descriptions 15

### www.si-gate.com

Si-Gate X-1500 Reference guide Revision 1.0 13.07.2005

© 2005 Si-Gate GmbH. All rights reserved.

Si-Gate, Si-Gate GmbH, and the Si-Gate logo are are trademarked property and may not be used with out the written permision of Si-Gate GmbH.

Notice: Si-Gate GmbH reserves the right to make changes in the hardware, software, packaging and any accompanying documentation without prior written notice.