## SPECTRUM SIGNAL PROCESSING by Vecima

# Wideband Digital Receiver/Digitizer Module VPX-1151

#### **Product Overview**

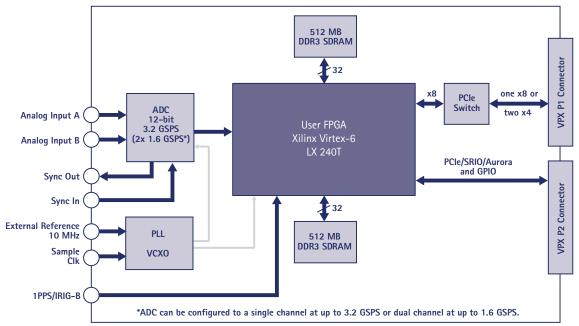

The VPX-1151 is an ultra high-speed digitizer and processing solution that enables direct RF-to-Digital conversion between 100 MHz and 3 GHz.

It complies with OpenVPX (VITA 65), the architecture framework that defines system-level VPX interoperability for multivendor, multimodule systems.

#### **Features**

- One 3.2 GSPS 12-bit ADC channel (or two channels at 1.6 GSPS)

- ADC input bandwidth up to 2.8 GHz enables bandpass sampling (Second Nyquist zone)

- Supports multi-board synchronization

- Support for phase coherent sampling\*

- Xilinx Virtex-6 LX240T User FPGA

- 1 GB DDR3 SDRAM (2 banks of 512 MB, 1066 Mbps)

- PCI Express x8 Gen 2 (VITA 42.3) (4 GB/s full-duplex)

- General purpose digital I/O including high speed serial

- Drivers and Linux SDK, API, FPGA interfaces included

- Digital downconverter (DDC) IP available

- Air-cooled, rugged conduction-cooled available

- \* See future options section of this datasheet

### **Applications**

- SIGINT (COMINT/ELINT)

- Joint Airborne SIGINT Architecture (JASA) IF Digitizer/processor

- RADAR

- Satellite Receiver

- Electronic Support Measures (ESM)

- Spectral Analysis

- Software Defined Radio (SDR)

- High-Speed Test and Measurement

- Wireless Set-Top Box Development

- Wideband Sensing for Cognitive Radio

- Channel Measurement and Characterization

VPX-1151 Block Diagram

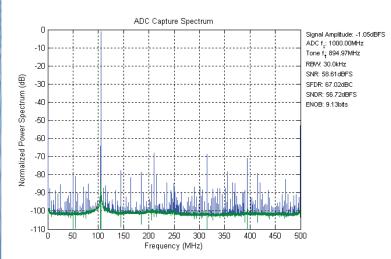

Sample spectral plot for 895 MHz input signal at 1.0 GSPS

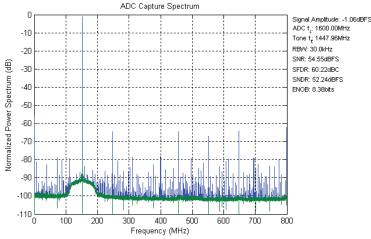

Sample spectral plot for 1448 MHz input signal at 1.6 GSPS

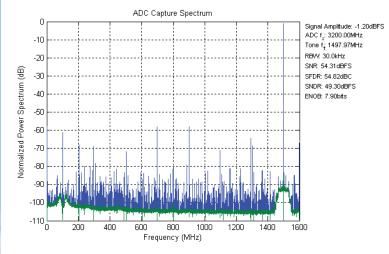

Sample spectral plot for 1498 MHz input signal at 3.2 GSPS

#### Specifications

|                                                                                                                                       |                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                                                             |                            |                            |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|

| User Programmable FPGA<br>Memory<br>Internal Sample Clock                                                                             |                                                                                                  | 3U OpenVPX (VITA 65) Module Compatible with Slot Profiles MOD3-PAY-1D-16.2.6-1, MOD3-PAY-1D-16.2.6-2, MOD3-PAY-2F-16.2.7-1, and MOD3-PAY-2F-16.2.7-2 Xilinx Virtex-6 LX240T-2 (LX130T, LX195T, LX365T, SX315T, SX475T are available as options) 1GB DDR3 SDRAM (2 banks of 512 MB each, 1066 Mbps) 1.6 GHz VCSO (Contact Spectrum for other frequencies) 10 MHz clock reference (+/- 2.0 ppm) |                            |                            |

| analog I/O ]                                                                                                                          |                                                                                                  | National Semiconductor ADC12D1600 12-bit @ 3.2 GSPS single channel or dual channel                                                                                                                                                                                                                                                                                                            |                            |                            |

| [ analog 1/O ]                                                                                                                        |                                                                                                  | at 1.6 GSPS                                                                                                                                                                                                                                                                                                                                                                                   |                            |                            |

| ADC Input AC coupled, single-ended Full scale input: 0 dBm 50 ohms typical Analog full power bandwidth: 5 MHz to 2.8 GHz (AC coupled) |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |

|                                                                                                                                       | ADC Characterization (typical)                                                                   | 895 MHz Fin with 1.0 GSPS                                                                                                                                                                                                                                                                                                                                                                     | 1448 MHz Fin with 1.6 GSPS | 1498 MHz Fin with 3.2 GSPS |

|                                                                                                                                       | (typical)                                                                                        | ADC SFDR = 67.0 dBc                                                                                                                                                                                                                                                                                                                                                                           | ADC SFDR = 60.2 dBc        | ADC SFDR = 54.8 dBc        |

|                                                                                                                                       |                                                                                                  | ADC SNR = 58.6 dBFS                                                                                                                                                                                                                                                                                                                                                                           | ADC SNR = 54.5 dBFS        | ADC SNR = 54.3 dBFS        |

|                                                                                                                                       |                                                                                                  | ADC ENOB = 9.1 Bits                                                                                                                                                                                                                                                                                                                                                                           | ADC ENOB = 8.4 Bits        | ADC ENOB = 7.9 Bits        |

|                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |

| [ external interfaces ]                                                                                                               | External Reference Clock<br>External Sampling Clock<br>GPS Timing Reference<br>Sync Input/Output | SSMC 50 ohms, 0 dBm typical SSMC 50 ohms, 0.75 - 1.6 Vpp 10 MHz clock reference SSMC 50 ohms, -3 dBm typical SSMC 50 ohms, 1PPS/IRIG-B TTL/LVTTL Twinax 100 ohms differential connector PCIe Gen 2: one x8 link or two x4 links, providing 4 GB/s (full-duplex) bandwidth to VPX P1 connector Configurable connection to VPX P2 connector: GPIO (1 pair LVDS clock with 16 pairs LVDS data    |                            |                            |

|                                                                                                                                       | JTAG Connection                                                                                  | and 4 single-ended LVTTL) plus PCIe Gen 2 x8 (can be configured for SRIO or Aurora*) JTAG connector for Virtex-6 FPGA, Xilinx Chipscope debugger compatible                                                                                                                                                                                                                                   |                            |                            |

| [ compatibility ]                                                                                                                     | Supported Host OS                                                                                | RedHat Enterprise Linux 5.3                                                                                                                                                                                                                                                                                                                                                                   |                            |                            |

| [ development software ]                                                                                                              | Application Libraries<br>FPGA Code Development                                                   |                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |

|                                                                                                                                       | HDL Coding Language                                                                              | VHDL or Verilog                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |

| [ electrical ]                                                                                                                        | Supply Voltage (DC)<br>Power estimate                                                            | +3.3V, VPWR (5V/12V)<br>20W (typical)                                                                                                                                                                                                                                                                                                                                                         |                            |                            |

| [ environmental ]                                                                                                                     | Shock and Vibration<br>Humidity<br>RoHS                                                          | Industrial conduction cooled -40 to 70 C card edge<br>Conduction cooled version VITA-47 level CC3 tested in accordance with MIL-STD-810F                                                                                                                                                                                                                                                      |                            |                            |

| [ ordering information ]                                                                                                              |                                                                                                  | VPX-1151 Quickstart Kit for VPX 3U Air-Cooled (includes software and documentation)<br>VPX-1151-CAC-V6LX240T-2-1GB 12b 3.2 GSPS ADC                                                                                                                                                                                                                                                           |                            |                            |

| [ future options** ]                                                                                                                  | Memory<br>ADC input<br>Multi-board Sync<br>*SRIO/Aurora                                          | 12-bit @ 3.6 GSPS single channel or dual channel at 1.8 GPSPS 12-bit @ 2.0 GSPS single channel or dual channel at 1.0 GPSPS 2 GB DDR3 SDRAM (2 x 1 GB banks) DC coupled Firmware to support phase coherent sampling Software and FPGA support VxWorks, Windows                                                                                                                                |                            |                            |