# High Linearity Wideband RF-to-Digital Transceiver RF-7102

### **Features**

- Integrated RF and Digital IF Processing in a single 3U OpenVPX slot

- High linearity, wideband RF Transceiver, 20 MHz to 3.0 GHz

- 14-bit ADC 490 MSPS, 16-bit DAC 980 MSPS

- Fast-frequency hopping up to 3000 hops/sec

- Up to 200 MHz Receiver analog bandwidth

- Up to 400 MHz Transmitter analog bandwidth

- Xilinx Virtex-5 SX95T-2 User FPGA for flexible IF signal processing

- PCI Express (PCIe) connection to host processor

- Software drivers and API, FPGA interface libraries, and example code included

- Digital Down Converter (DDC) and Digital Up Converter (DUC) IP included

- Rugged conduction- or air-cooled form factors available

- Designed to operate with host SBC, VPX-1131, VPX-1151, and VPX-8320 as part of Spectrum's SDR-7000 family

- Not subject to US ITAR control

## **Applications**

External

harmonic

reiection filter

ADC

ADC

DAC

CDAC <

**CGPIO**

`CGPIO

Front Pane

Audio.

Analog Control,

1PPS, IRIG-B,

Sync, Trigger, Control

- Wideband Datalinks (eg. UAV, UGV, USV)

- Ground Mobile Communications

- Air-to-Ground Communications

- Communications Electronic Warfare

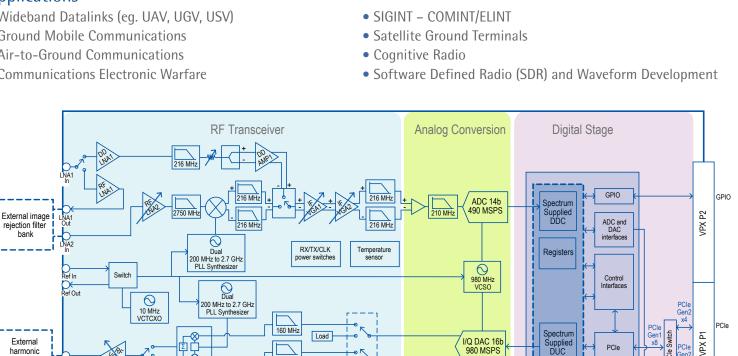

RF-7102 RF-to-Digital Transceiver System Block Diagram

ADC/ DAC

100 ksps

160 MHz

Modulator

PCIe

16 MB Boo

FPGA (V5SX95T-2)

User Region

512 MB SDRAM

# Specifications

| [ general ]             |                                                  | Single channel full-duplex RF transceiver with Xilinx Virtex-5 FPGA                                                                                    |

|-------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Form Factor                                      | 3U OpenVPX (VITA 65) Module                                                                                                                            |

|                         |                                                  | Compatible with Module Profiles MOD3-PAY-1D-16.2.6-1, MOD3-PAY-1D-16.2.6-2, MOD3-PAY-2F-16.2.7-1, and MOD3-PAY-2F-16.2.7-2. For other module profiles, |

|                         |                                                  | please contact Spectrum.                                                                                                                               |

| [ RF - Receiver ]       | Receiver Type                                    | Single-conversion superheterodyne with IF digitizer (above 200 MHz)                                                                                    |

| [ necerte. ]            | neceiver 15pc                                    | Direct digitizing receiver (below 200 MHz), with mixer bypassed                                                                                        |

|                         | Input Frequency Range                            | 20 MHz to 3.0 GHz                                                                                                                                      |

|                         |                                                  | User programmable from 20 MHz to 200 MHz                                                                                                               |

|                         |                                                  | 200 MHz LPF (BPF and other options, contact Spectrum)                                                                                                  |

|                         |                                                  | 200 MHz standard, other bandwidths available<br>20 μs (dual switching synthesizer)                                                                     |

|                         |                                                  | 3,000 hops/sec with 10:1 dwell-to-tune time ratio                                                                                                      |

|                         |                                                  | 400 kHz, smaller step sizes achieved digitally                                                                                                         |

|                         | Maximum RF Input Power Level                     |                                                                                                                                                        |

|                         |                                                  | +10 dBm at -20dBm input                                                                                                                                |

|                         | Gain Adjustment                                  | RF mode: > 80 dB in 0.5 dB steps<br>Direct digitizing mode: > 65 dB in 0.5 dB steps                                                                    |

|                         | Noise Figure                                     | Better than 6 dB over entire range 20 MHz-3.0 GHz with image rejection filter                                                                          |

|                         |                                                  | 10 MHz, +/- 2.0 ppm @ room temp                                                                                                                        |

| Spurious Fi             | ree Dynamic Range (SFDR) (typical)               | Direct Digitizing Mode (input power at -20 dBm)                                                                                                        |

|                         |                                                  | 20 MHz to 200 MHz: -70 dBc                                                                                                                             |

|                         |                                                  | RF Mode (input power at -30 dBm) 200 MHz to 2.7 GHz: -70 dBc                                                                                           |

|                         |                                                  | 2.7 GHz to 3.0 GHz: -60 dBc                                                                                                                            |

|                         |                                                  | Note: -1 dBFS desired signal                                                                                                                           |

|                         | •                                                | Intersil ISLA214P50 14 bit at 490 MSPS                                                                                                                 |

|                         |                                                  | User-supplied external filter. Contact Spectrum for custom filtering.                                                                                  |

| [ RF - Transmitter ]    | Transmitter Type                                 | Direct up-conversion (I/Q) above 200 MHz                                                                                                               |

|                         | Output Eroquonay Panga                           | Direct DAC output to amplifier below 200 MHz, with quadrature modulator bypassed                                                                       |

|                         | Output Frequency Range<br>Output Power (typical) | -25 dBm to +5 dBm CW, in 0.5 dB steps                                                                                                                  |

|                         | OIP3 @ -5 dBm Output Power                       |                                                                                                                                                        |

|                         |                                                  | 200 MHz - 2.2 GHz: >30 dBm                                                                                                                             |

|                         | D4 ID                                            | 2.2 - 3.0 GHz: >23 dBm                                                                                                                                 |

|                         |                                                  | +18 dBm at 800 MHz<br>-140 dBm/Hz measured at 805 MHz in presence of a full power output CW signal                                                     |

|                         | 11001                                            | at 850 MHz                                                                                                                                             |

|                         | Adjacent Channel Leakage Ratio                   | -67 dBc at full output power, 800 MHz, 5 MHz bandwidth NPR signal                                                                                      |

|                         | Non-Harmonic Output Spurious                     | -60 dBc at 1.4 GHz, Zero IF (I/Q)                                                                                                                      |

|                         |                                                  | Analog Devices AD9122 16 bit interpolating DAC at 980 MSPS                                                                                             |

|                         |                                                  | Zero IF (I/Q) or Complex IF 20 µs (dual switching synthesizer)                                                                                         |

|                         | Maximum Hop Rate                                 | 3,000 hops/sec with 10:1 dwell-to-tune time ratio                                                                                                      |

|                         |                                                  | 400 kHz, smaller step sizes achieved digitally                                                                                                         |

|                         | Harmonic Rejection                               | User-supplied external filter. Contact Spectrum for custom filtering.                                                                                  |

| [ IF Processing ]       | User FPGA                                        | Virtex-5 SX95T-2 (optional V5LX155T). SX95T-2 has 94,208 logic                                                                                         |

|                         | TDC : T                                          | cells, 640 DSP48E slices, and 8,784 kb total BRAM                                                                                                      |

|                         | FPGA IP                                          | DDC and DUC included (user programmable IF bandwidth, IF frequency, and                                                                                |

|                         | Memory                                           | decimation/interpolation) 512 MB DDR2 SDRAM                                                                                                            |

| [ external interfaces ] |                                                  | PCIe from host SBC                                                                                                                                     |

| [ external interfaces ] |                                                  | 6 SMA, 50-ohm, single-ended (see block diagram)                                                                                                        |

|                         | Analog GPIO                                      | 2x 12b 100 kSPS DAC, 2x 12b 100 kSPS ADC. Software support as a future option.                                                                         |

|                         | Trigger/Interrupt Interface                      |                                                                                                                                                        |

|                         | High-Speed Serial Interfaces                     | One PCIe Gen1 x8 from FPGA to PCIe switch (2 GB/s full duplex) Two PCIe Gen2 x4 from PCIe switch to AMC backplane (2 GB/s full-duplex per port)        |

|                         |                                                  | 2 bi-directional high-speed serial lanes (can be configured for SRIO or Aurora*)                                                                       |

|                         | FPGA Programming                                 | Programming via JTAG or load from onboard 16 MB Flash                                                                                                  |

|                         | FPGA Debug                                       | Debug via JTAG with Xilinx JTAG device                                                                                                                 |

|                         |                                                  | 8x LVDS pairs, 11x 3.3V LVTTL (5 are 5V tolerant), all via VPX P2 connector                                                                            |

|                         | Co-Ax GPIO                                       | Two co-ax single-ended available through the front panel (3.3V, 5V tolerant)                                                                           |

|                         |                                                  | (1PPS, IRIG-B, sync, trigger, control)                                                                                                                 |

|                         |                                                  |                                                                                                                                                        |

| [ electrical/mechanical ] | Supply Voltage (DC)               | 5V and +12V                                                                         |

|---------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

|                           | Power Estimate                    |                                                                                     |

|                           | Size                              | 3U OpenVPX form factor                                                              |

| [ environmental ]         | Temperature                       | 0 to +50 degrees C (air-cooled)                                                     |

|                           |                                   | -40 to +70 degrees C (conduction-cooled)                                            |

|                           | Shock and Vibration               | Conduction-cooled version: ANSI/VITA 47, Level ECC3                                 |

|                           |                                   | Conformal coating available on request.                                             |

|                           |                                   | 5 of 6 compliant (Pb solder exemption).                                             |

|                           | MTBF                              | Estimated at >300,000 hours (GB, GC, 30 deg C), per MIL-HDBK-217 FN2                |

|                           |                                   | Parts Count Method, Relex v8.0                                                      |

| [ software ]              | Application Libraries             | quicComm™ Software Development Kit with APIs and examples running on Host SBC       |

|                           | Operating System                  | Green Hills INTEGRITY 11 with MULTI 6 IDE                                           |

|                           |                                   | Red Hat Enterprise Linux 6.5                                                        |

|                           | Digital Up/Down Converter         | FPGA-based DDC and DUC provided featuring polyphase filter with variable bandwidth. |

|                           |                                   | User can control IF bandwidth, IF frequency and decimation/interpolation with       |

|                           |                                   | software to achieve frequency steps as small as 117 Hz.                             |

|                           | SCA BSP                           | Software Communications Architecture Board Support Package for NordiaSoft SCARI     |

|                           |                                   | SCA Suite                                                                           |

|                           | CORBA Object Request Broker (ORB) | OIS ORBExpressRT                                                                    |

| [ host SBC ]              |                                   | • Freescale QorIQ P3041 CES Creative Electronic Systems RIOV-2473 running           |

|                           |                                   | Green Hills INTEGRITY 11, with RTM-6240 rear transition module.                     |

|                           |                                   | For more information, visit www.ces.ch.                                             |

|                           |                                   | • Intel i7 SBC running Red Hat Enterprise Linux 6.5                                 |

|                           |                                   | • For other SBCs, please contact Spectrum.                                          |

| [*future options]         |                                   | Contact Spectrum Sales for options listed in this section.**                        |

| •                         |                                   | V5LX155T                                                                            |

|                           | Analog GPIO                       | Software support for low speed ADC and DAC, e.g., Audio, Analog Control/Sensors     |

|                           | Internal Analog IF Filtering      | 70 MHz BPF, 140 MHz BPF, or custom filtering, contact Spectrum                      |

|                           |                                   | Configure 2 bi-directional high-speed serial lanes for SRIO or Aurora               |

|                           |                                   | Contact Spectrum for external filter options                                        |

|                           | 9                                 | Built-In-Test (BIT)                                                                 |

|                           |                                   | Contact Spectrum to discuss alternative host SBCs                                   |

|                           | Operating System                  | Wind River VxWorks                                                                  |

#### Notes:

• Individual specifications on this datasheet are subject to change without notice. Do not specify compliance with this document.

fax +1/604.421.1764

## **Appendix**

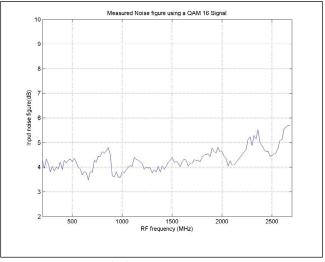

Figure 1. Noise Figure (NF) versus RF frequency in RF mode at 65 MHz IF, at -90 dBm input power (typical).

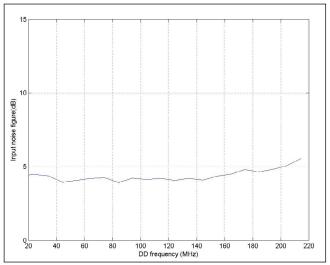

Figure 2. Noise Figure (NF) versus RF frequency in Direct Digitizing (DD) mode at -90 dBm input power (typical).

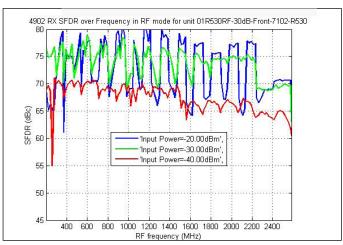

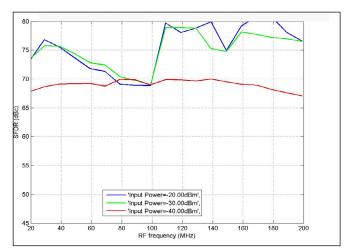

Figure 3. SFDR versus RF frequency in RF mode at 3 different input power levels (typical).

Figure 4. SFDR versus RF frequency in DD mode at 3 different input power levels (typical).

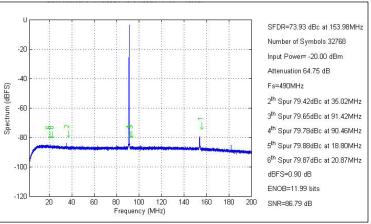

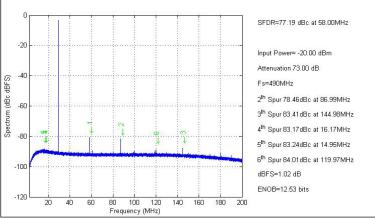

Figure 5. SFDR detail for RF frequency 301 MHz, IF 91 MHz at -20 dBm input power in RF mode (typical).

Figure 6. SFDR detail for RF frequency 31 MHz at -20 dBm input power in DD mode (typical).

www.spectrumsignal.com

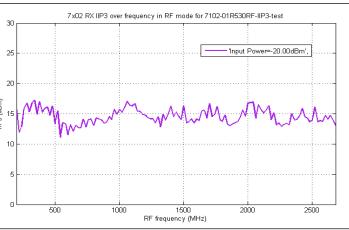

Figure 7. Receiver IIP3 versus RF frequency at -20 dBm input power in RF mode (typical).

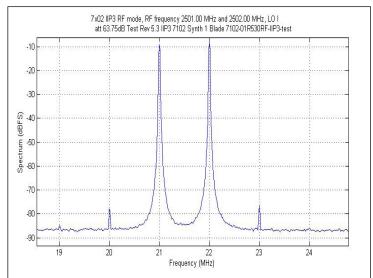

Figure 9. Receiver IIP3 detail for RF frequency 2501 MHz and 2502 MHz in RF mode (typical).

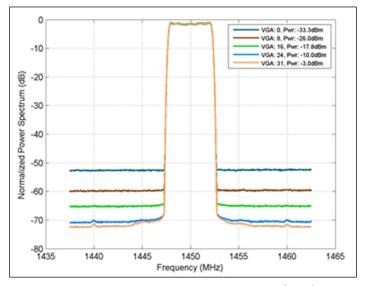

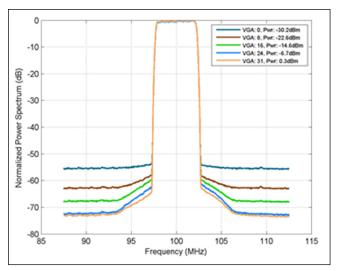

Figure 11. Transmitter Adjacent Channel Leakage Ratio (ACLR) at 1450 MHz in RF mode (typical).

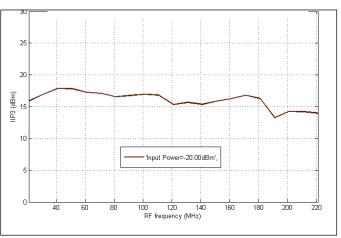

Figure 8. Receiver IIP3 versus RF frequency at -20 dBm input power in DD mode (typical).

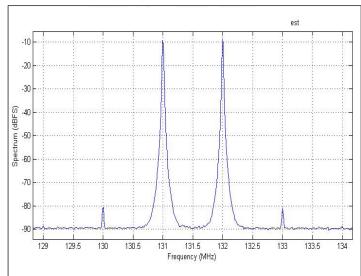

Figure 10. Receiver IIP3 detail for RF frequency 131 MHz and 132 MHz in DD mode (typical).

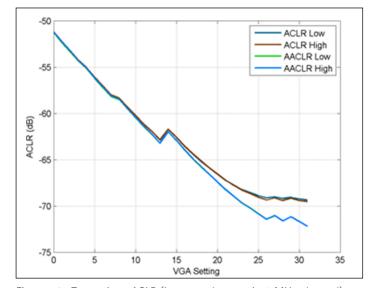

Figure 12. Transmitter ACLR (integrated power in 5 MHz channel) versus variable gain setting at 1450 MHz center frequency in RF mode (typical).

Figure 13. Transmitter ACLR at 100 MHz in DD mode (typical).

Figure 15. Transmitter output power flatness at LO frequencies of 300 MHz, 800 MHz, 1400 MHz, and 2700 MHz with IF swept from -100 MHz to +100 MHz (typical).

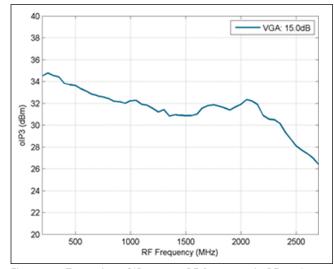

Figure 17. Transmitter OIP3 versus RF frequency in RF mode (typical).

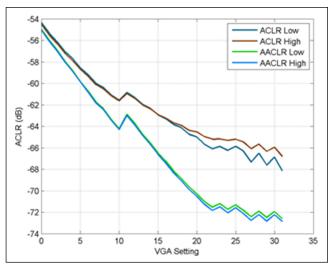

Figure 14. Transmitter ACLR (integrated power in 5 MHz channel) versus variable gain setting at 100 MHz center frequency in DD mode (typical).

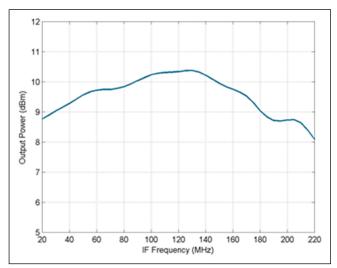

Figure 16. Transmitter output power flatness in DD mode (typical).

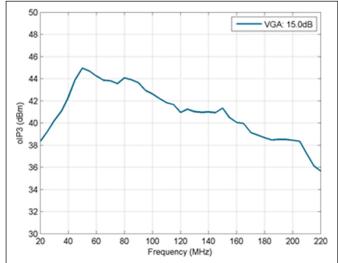

Figure 18. Transmitter OIP3 versus RF frequency in DD mode (typical).