## Hardent DSC Decoder IP

Hardent's IP portfolio offers customers ready-made solutions to accelerate product development and meet demanding time-to-market schedules.

Developed by a team of experienced FPGA and ASIC designers, Hardent's IP cores have undergone extensive verification and offer proven interoperability and compatibility.

## **Key Features**

- VESA Display Stream Compression (DSC) 1.2a compliant

- Supports all DSC 1.2a mandatory encoding mechanisms • MMAP, BP, MPP, and ICH

- Input buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

Up to 4K (4096x2160), 5K (UHD+), and 8K (FUHD)

- 8, 10, 12, 14, and 16 bits per video component

- YCbCr and RGB video output format

- 4:4:4, 4:2:2, and 4:2:0 native coding

- Resilient to bitstream corruption

- 3 pixels / clock internal processing architecture in 4:4:4

- 6 pixels / clock internal processing architecture in 4:2:2 and 4:2:0

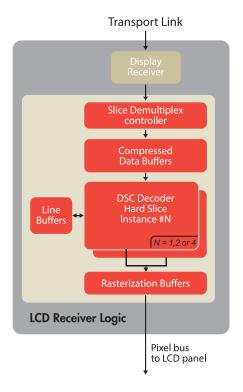

- Parameterizable number of parallel slice decoder instances (1, 2, or 4) to adapt to the capability of the technology and target display resolutions used

- Optional DSC features can be disabled to improve area

- 100% verification coverage based on UVM environment

- Verified against the VESA DSC 1.2a C model using a comprehensive test image library

- Backward compatible with DSC 1.1

## Deliverables

- Encrypted RTL source code IP core

- Functional and structural coverage reports

- Comprehensive integration guide

- Technical support and maintenance updates

## **Product Options**

- IP customization and integration services available on request

- Multi-project licenses available

- UVM verification bindable modules

DSC1.2-DEC\_prodbrief-v1.0

For additional information contact: info@hardent.com +1-514-284-5252 www.

vww.hardent.com